Writing and managing Tests

Contents are extracted from the Advanced UVM sessions by Verification Academy.

What is a test?

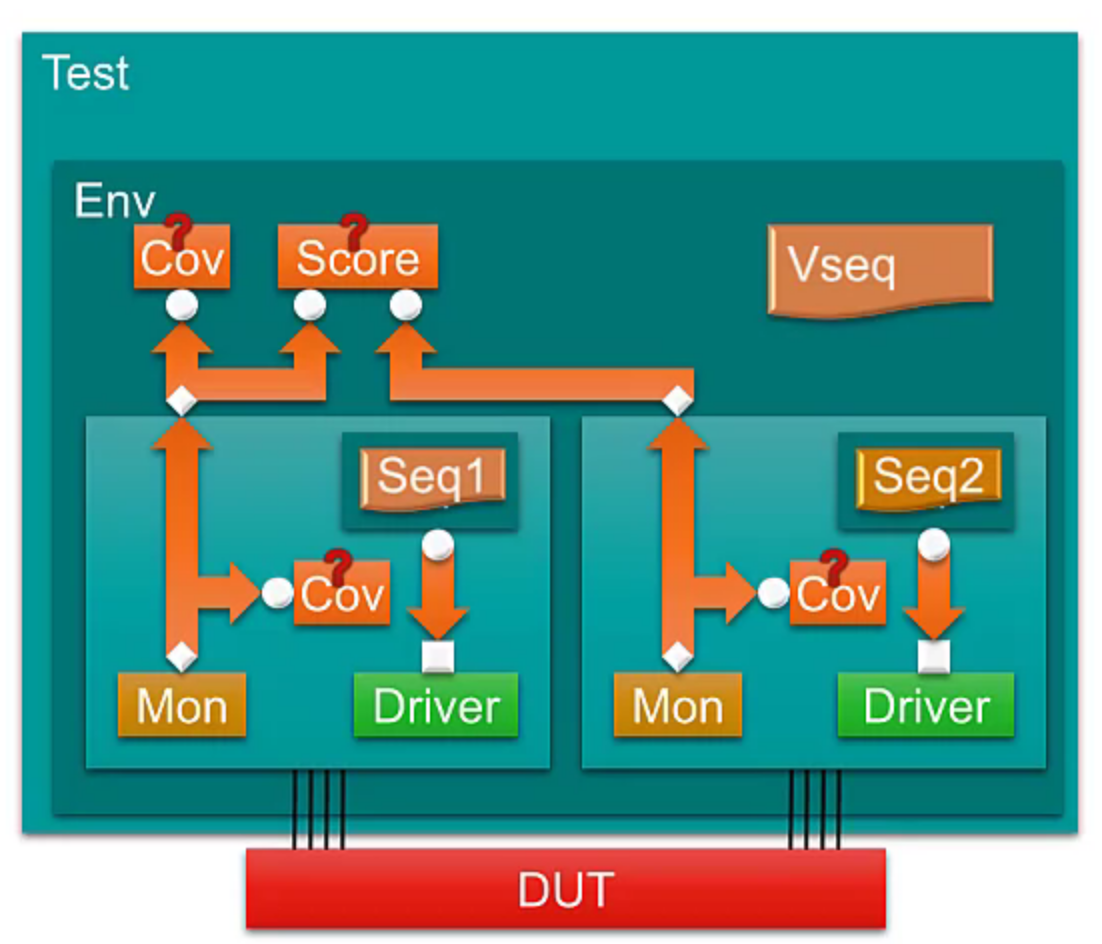

The environment is the “testbench”

- Defines what components are needed to verify the DUT

- Specifies defaults

The test’s job is to “tweak” the tesbench

- Configuration

- Factory overrides

- Additional sequences

The test’s other job is to ensure that the simulation ends

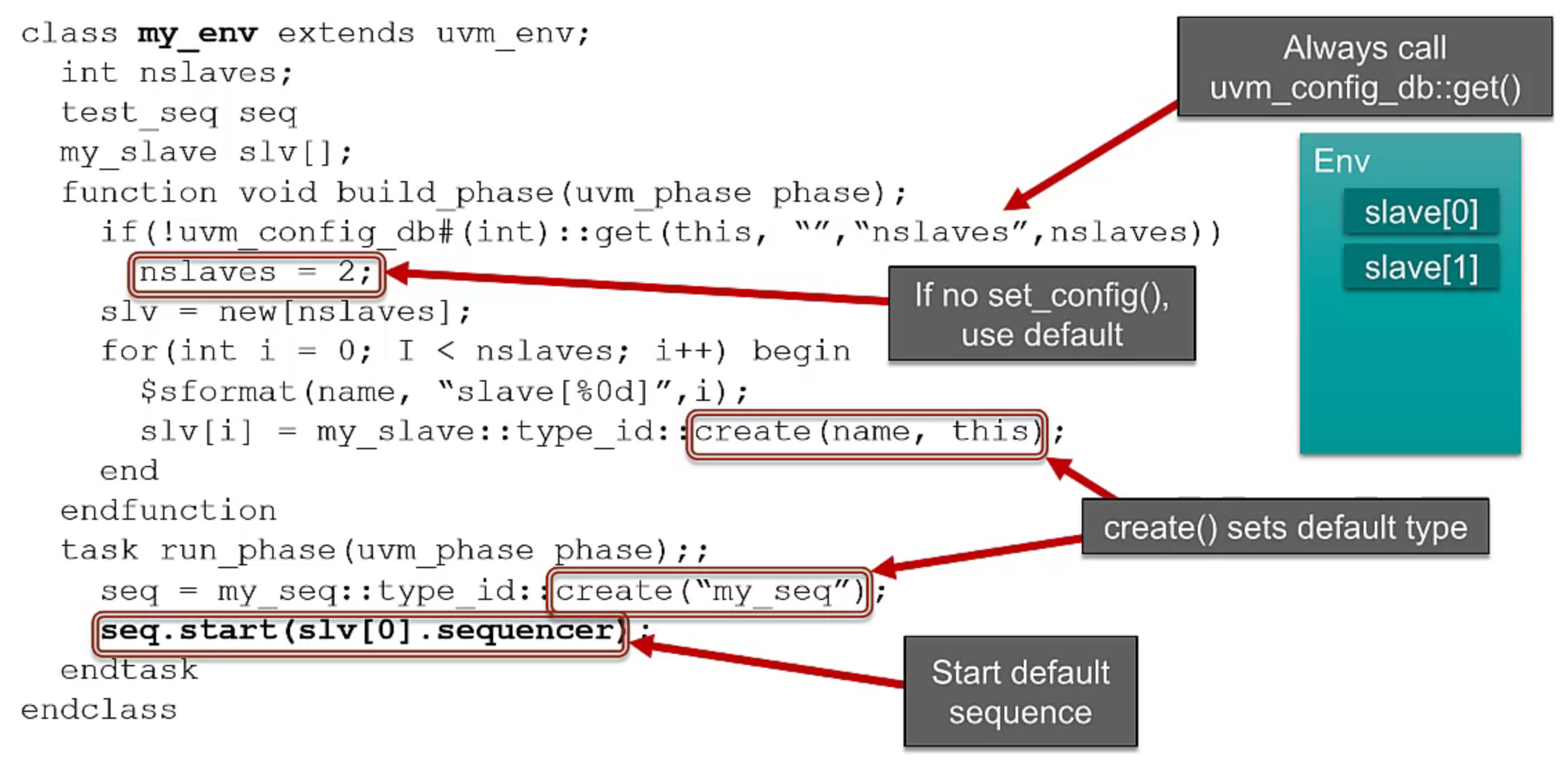

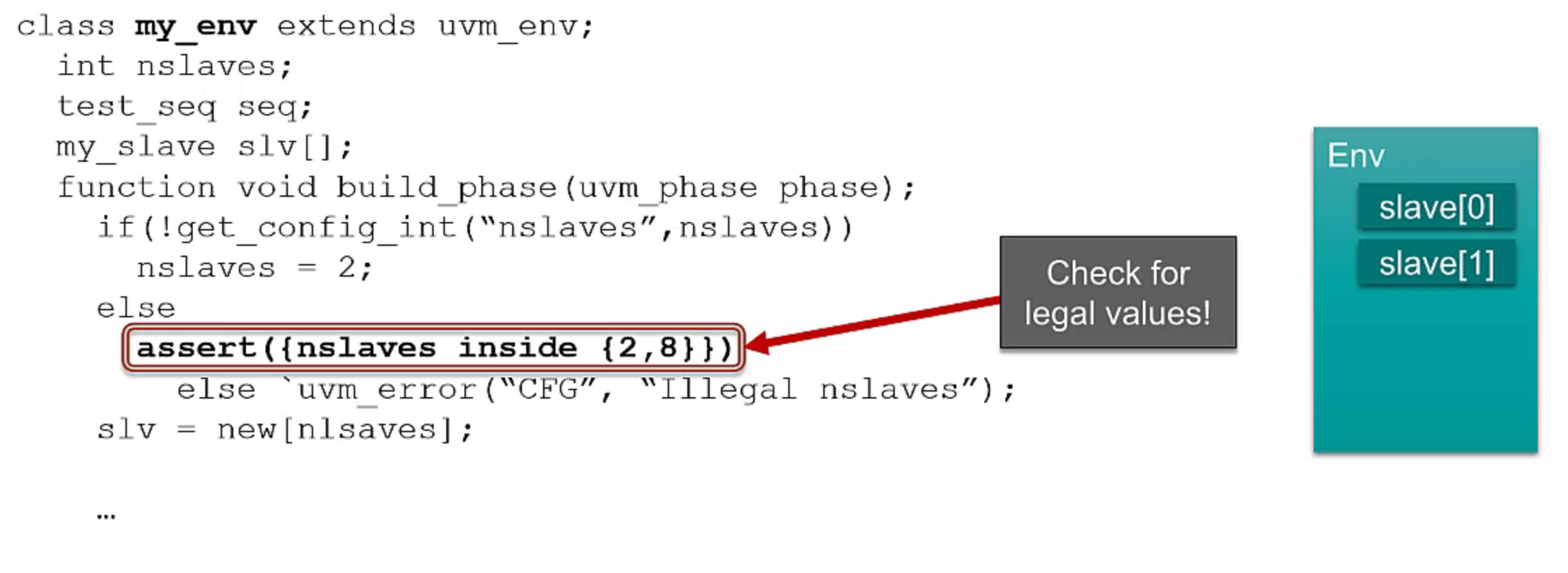

Defaults in UVM

Can add additional check to make sure the value pass by the configuration DB from the test is still legal

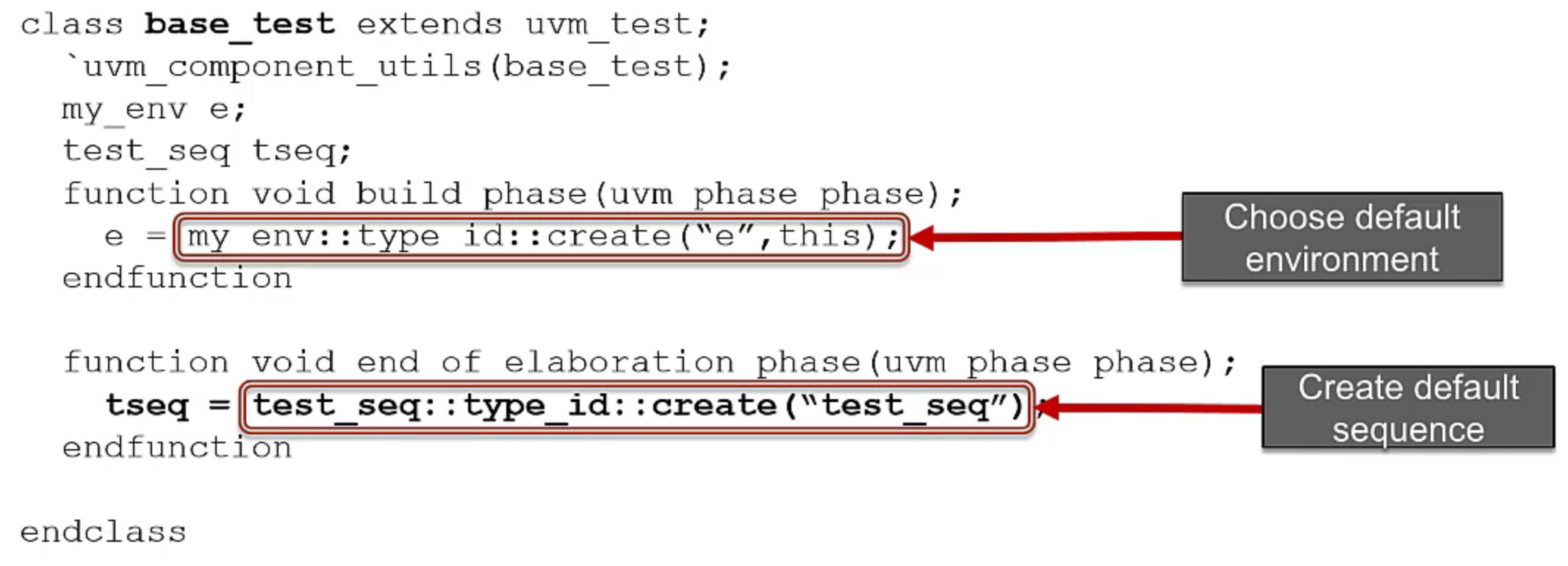

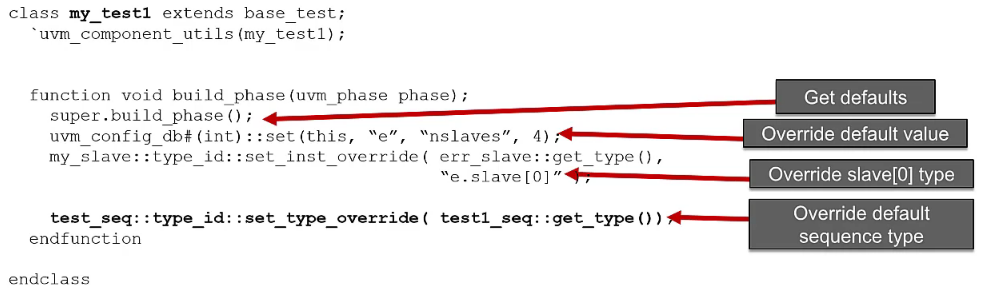

Use a Base Test to set defaults

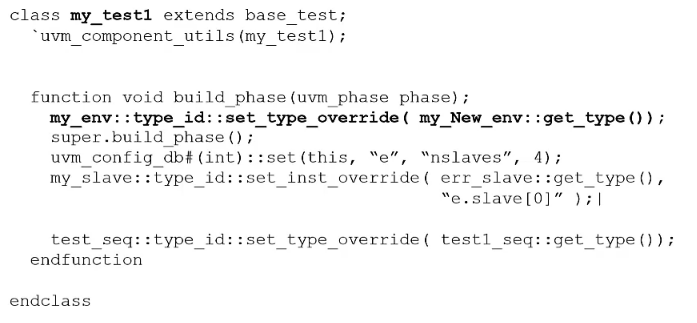

There is option to override the environment type, make sure to do factory override before calling

super.buildinside the extended test

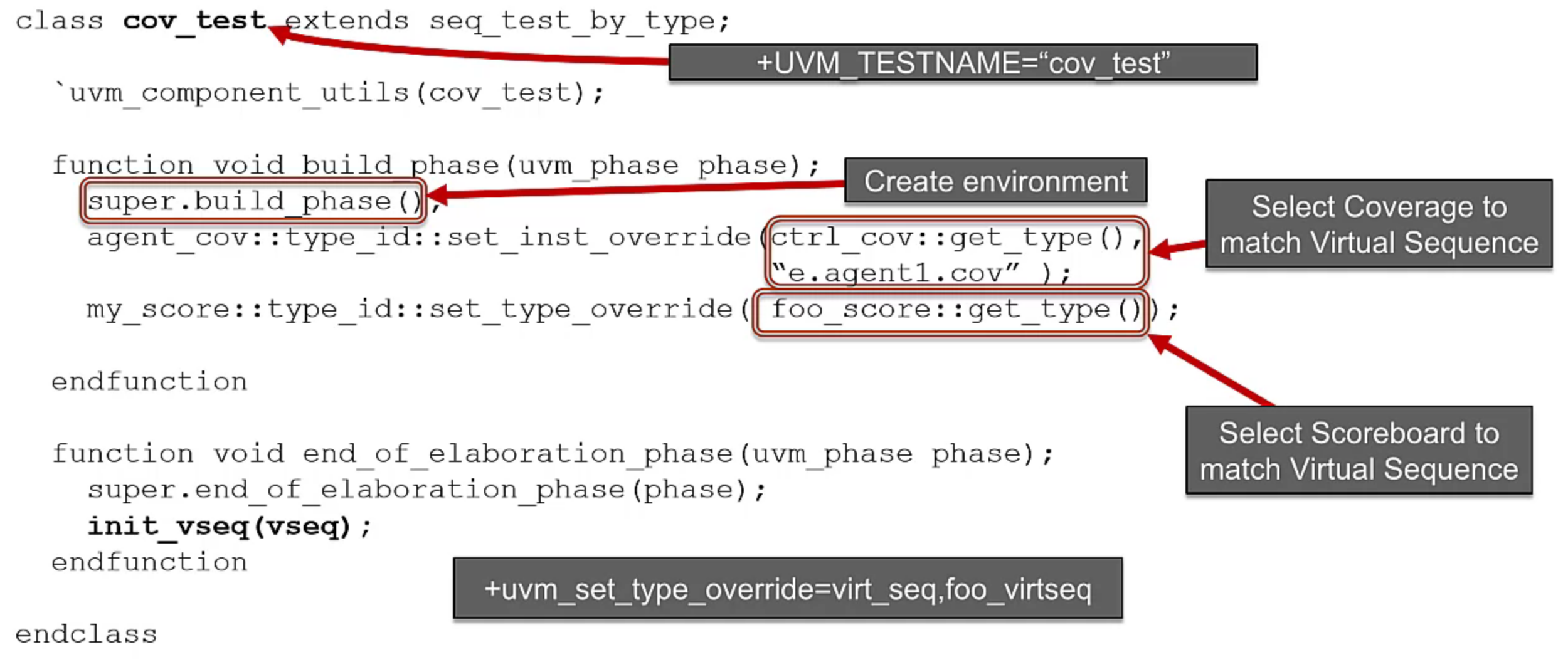

Extend Base Test to create a Test

To override the environment type as mentioned above:

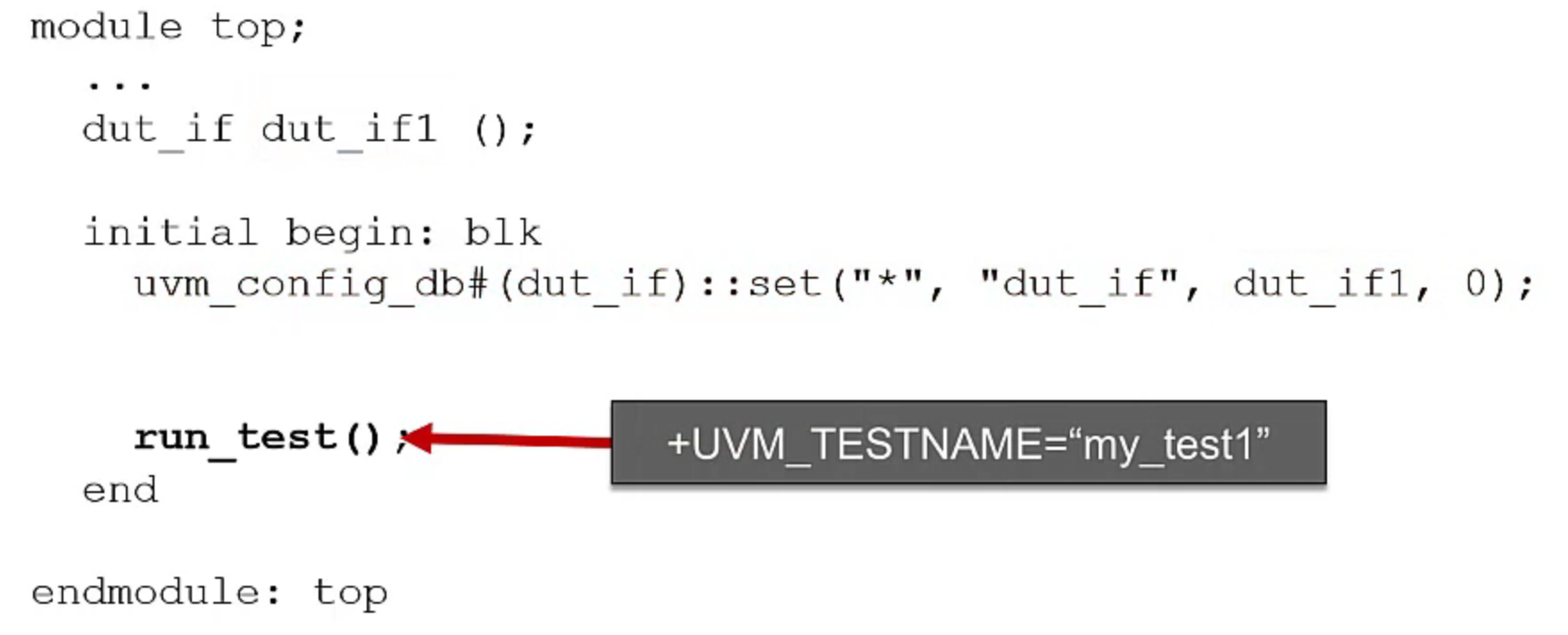

Set up and invoke test

Instantiate the DUT’s virtual interface and pass it down to the testbench through UVM config DB

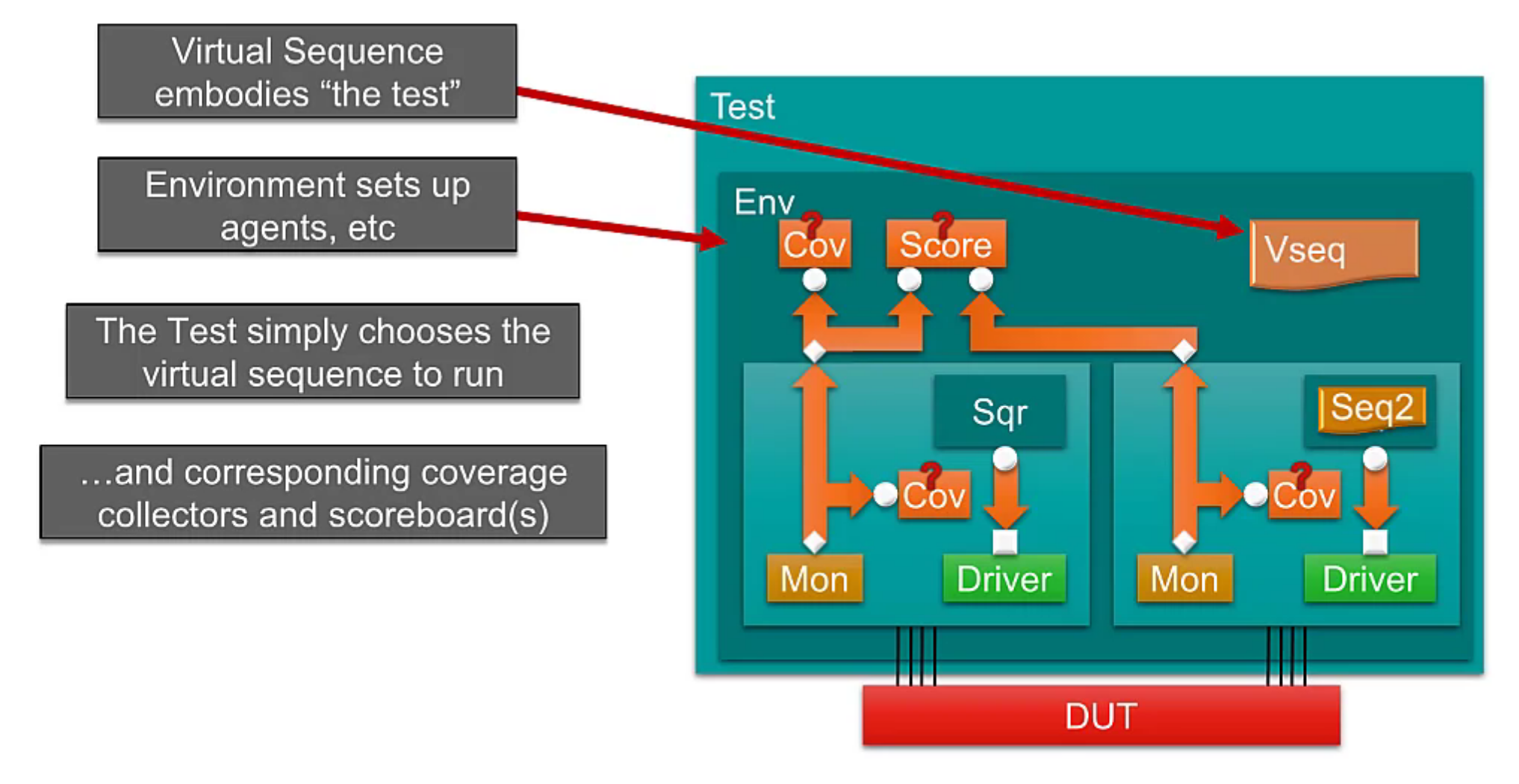

Complex environment, simple test

Simple Test

Extended Test

The virtual sequence can also be overridden using the

set_type_overridemethod → Explicit sequence type override

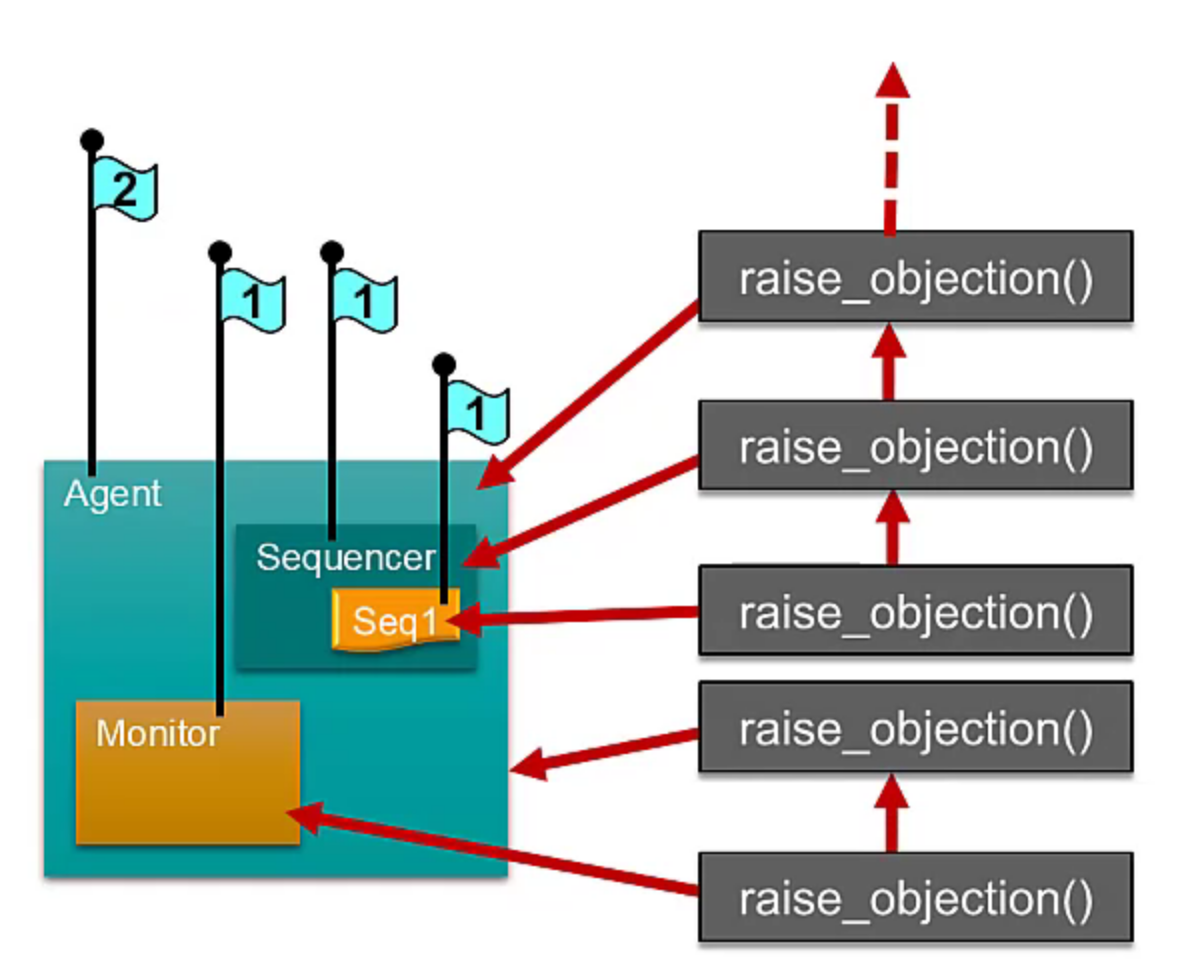

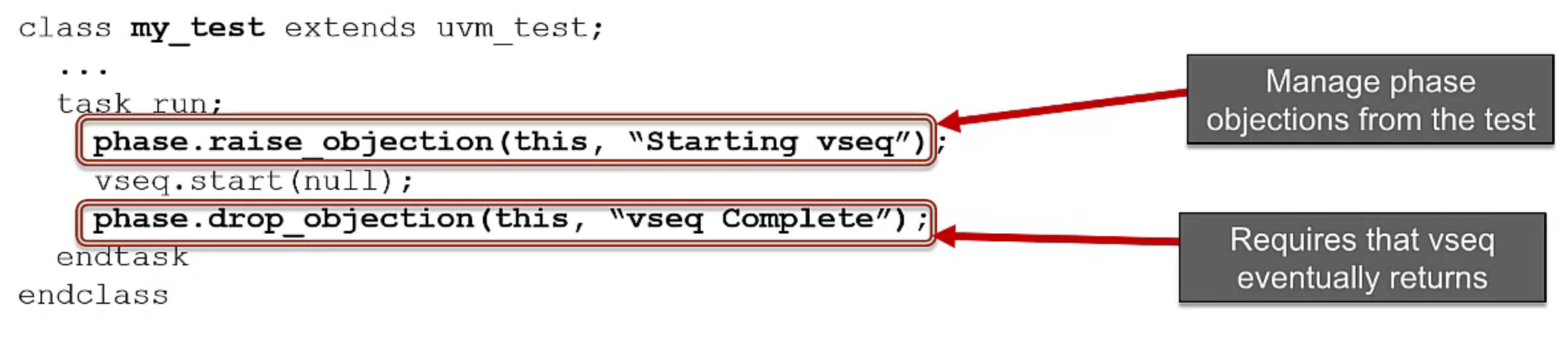

Managing Test Execution: Phase objections

Components or Sequences can raise or drop objections

Phase continues until all raised objections are dropped

An objection must be raised at the beginning of the phase

Objections are hierarchical

Objections are raised up the hierarchy by default

Sequencer’s objection + Monitor’s objection = 2 agent’s objections

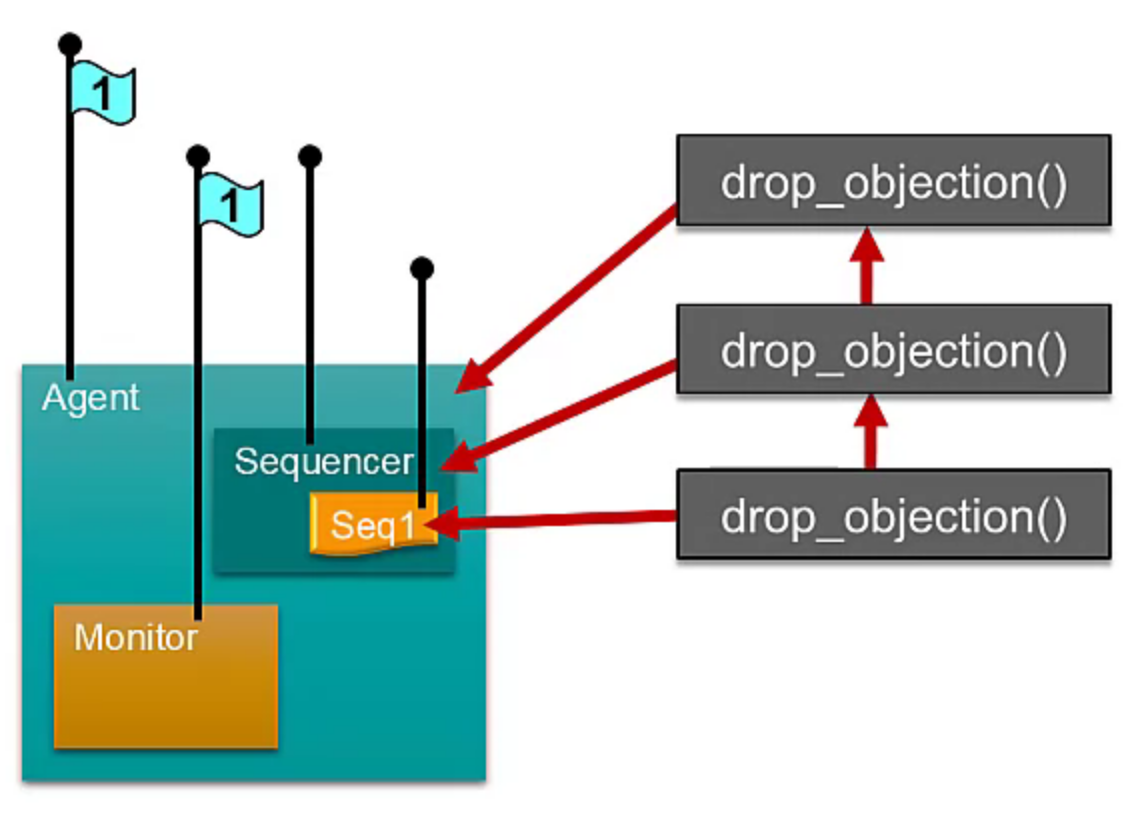

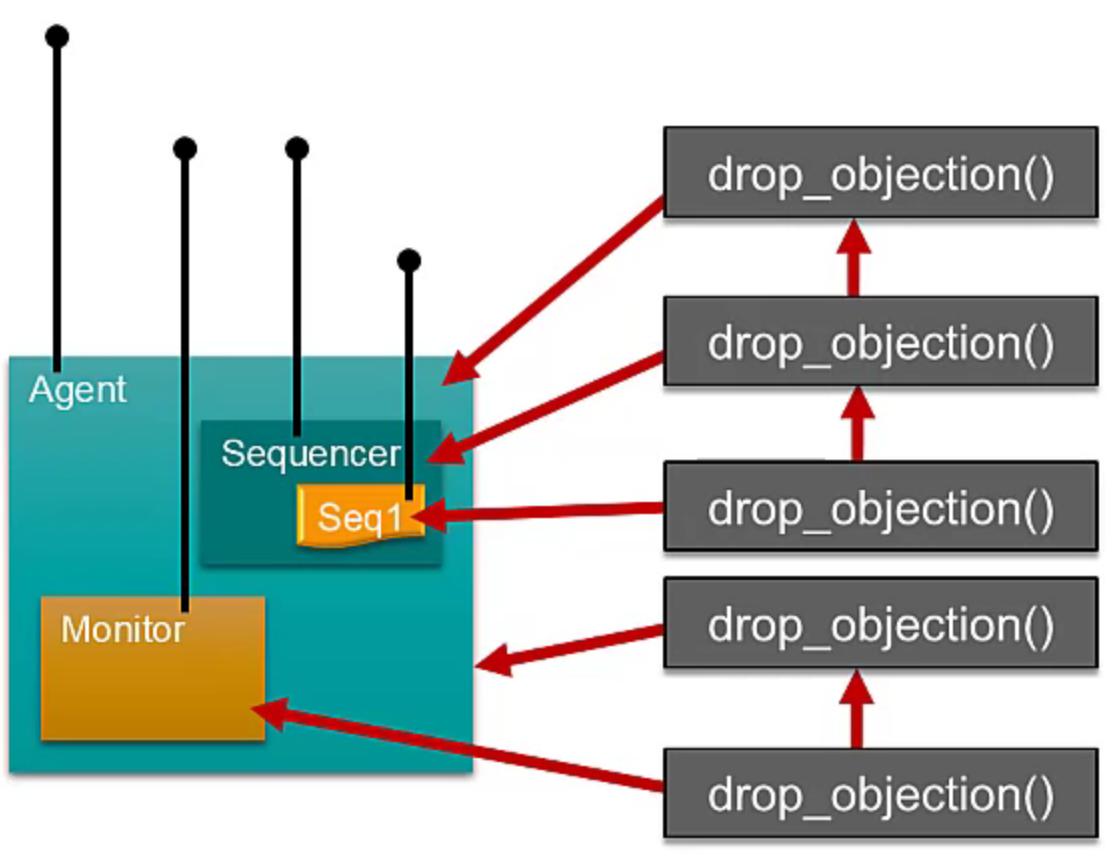

Objections are dropped hierarchically too

When a component’s count = 0, wait for drain_time to elapse

Recommendation

Raise and drop objections inside the test

Allows the test to determine when all the stimulus is complete and start dropping the objection

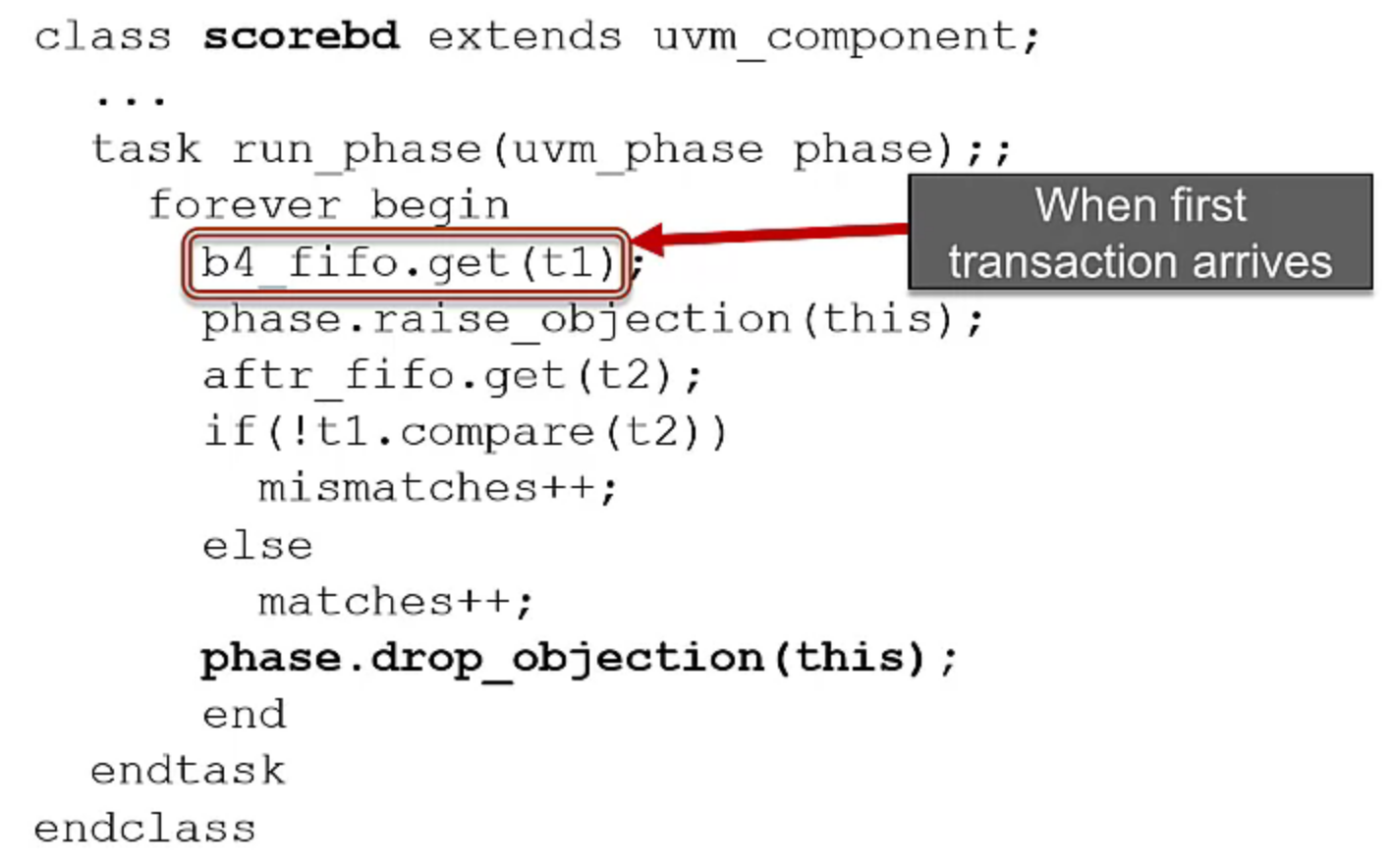

There might be cases where the objections is drop before the last transaction hasn’t finish processing yet

Using objections

Scoreboard recording transactions can raise an objection to prevent the test from ending early, make sure all the transactions has been recorded

Not recommended since it will introduce additional overhead

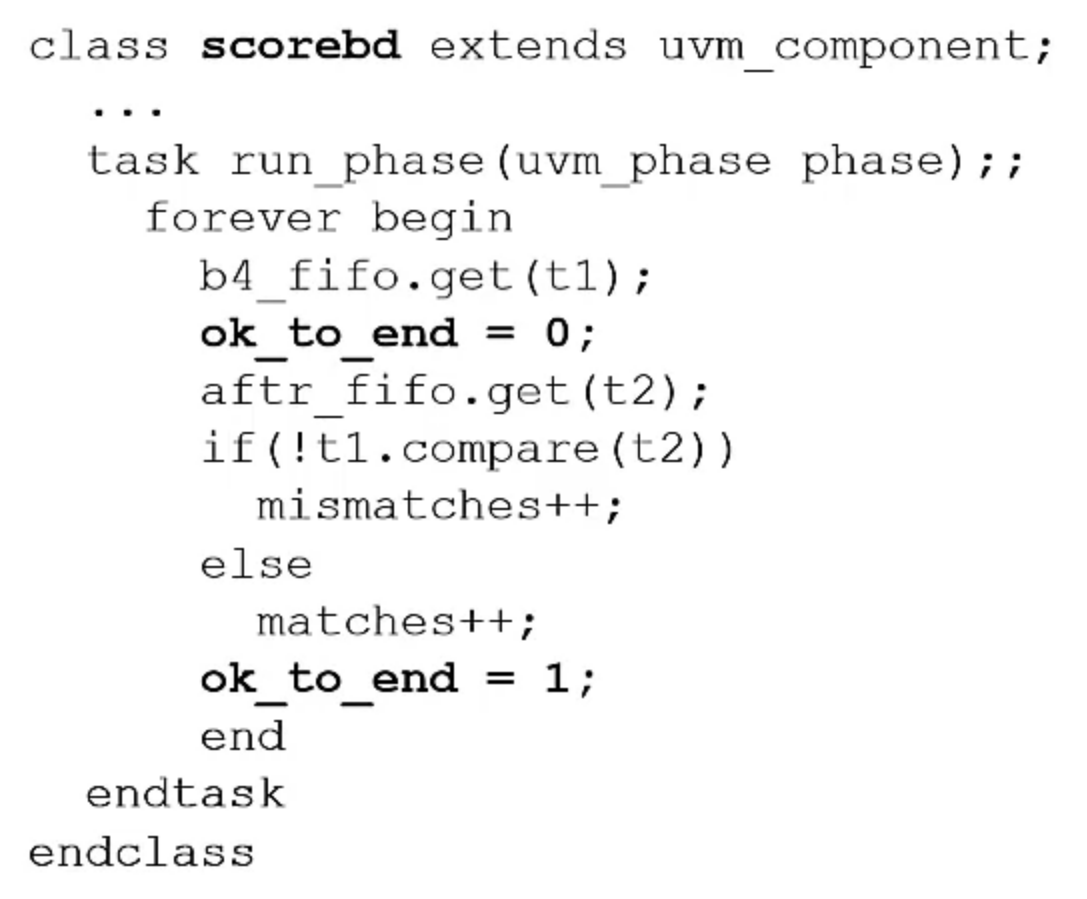

Alternative solution:

Recommendation: Objecting in a component

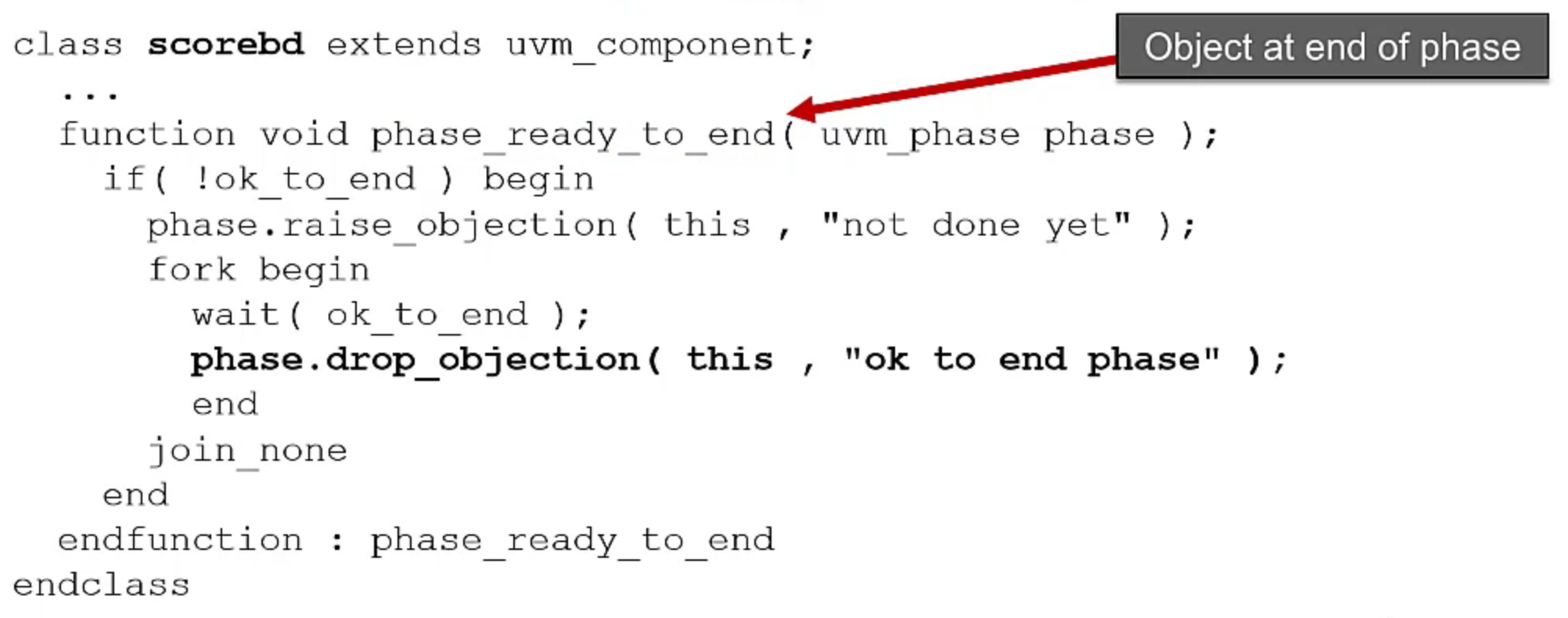

Using the provided method

phase_ready_to_endto do the objection before ending the phase

Summary